Que é SMPS?

Aprende o que é SMPS e o significado das diferentes clasificacións de eficiencia antes de escoller un SMPS para o teu ordenador.

Hai moitas capas diferentes para abordar DRAM. O DIMM é probablemente o máis coñecido, sendo un DIMM ( Dual In-line Memory Module ) unha memoria RAM. En última instancia, a memoria xestionase mediante un enderezo de fila e columna. Non obstante, hai moitas máis capas no medio. Accédese á memoria a través de canles. Cada canle é totalmente independente e pode transmitir datos ao mesmo tempo.

Nota: aínda que as canles son independentes, funcionan en bloque e están sincronizadas. É esencial asegurarse de que cada canle poboada funcione á mesma velocidade e teña os tempos exactos. Idealmente, todos os DIMM conectados deberían ser idénticos e dun kit. A RAM non idéntica pode causar problemas de estabilidade. Se se conectan DIMM de diferentes velocidades, o máis rápido limitarase á velocidade máis lenta.

Nun DIMM, tes un ou máis rangos de chips DRAM. Todos os chips dun rango están dirixidos á vez e son esencialmente presentados á CPU como un chip DRAM máis grande. Isto funciona porque os datos están repartidos por todos os chips DRAM nun rango. Por exemplo, unha canle ten un ancho de 64 bits e un chip DRAM ten un ancho de 8 bits. Necesítanse 8 chips DRAM para proporcionar 64 bits de datos aos pinos de datos. O rango defínese esencialmente polo chip select, que actúa como un bifurcador para os chips baixo o seu control. Cada chip ten varios bancos.

Banca en DRAM

Nun só chip DRAM, hai varios bancos. A especificación DDR4 asigna 4 bits a bancos de dirección, o que permite 16 bancos por chip DRAM. Cada banco é xeralmente independente e pode estar en calquera fase do ciclo de acceso/actualización. Todos os bancos teñen só un conxunto de pinos de datos. Esta configuración limita o chip DRAM a ter só un banco que transmite ou recibe datos por ciclo de reloxo. Tamén permite unha canalización forte, que, cunha carga suficiente, permite que eses pinos de datos estean activos na maioría dos ciclos de reloxo, se non en todos, en lugar de permanecer inactivos mentres se abre unha nova fila.

Outra cousa clave que hai que saber sobre os bancos é que están totalmente sincronizados a través dunha serie de chips DRAM. Esta sincronización é tan completa que se pode considerar que os bancos abarcan todos os chips DRAM do rango.

Un exemplo traballado

Usemos un exemplo; neste exemplo, unha operación de lectura pasa a un rango para acceder ao banco 2, fila 3, columna 4. Todos os chips DRAM do rango abrirán a fila tres, columna catro, no segundo banco. Cada un devolverá 8 bits de datos. A selección de chip que define o rango concatenará os datos que recibe no formato ancho de 64 bits da canle e enviarao ao controlador de memoria da CPU.

Levando o exemplo un pouco máis aló, ao mesmo tempo que o banco 2 xestiona a solicitude de lectura, o banco tres pode realizar unha operación de actualización. Ademais, un banco pode pechar a súa fila aberta para preparala para abrir unha nova. O banco 7 pode completar unha operación de lectura ao mesmo tempo. Non obstante, non pode enviar os datos ao mesmo tempo xa que todos os bancos comparten o mesmo conxunto de pinos de datos. O banco 7 debe esperar a que os pinos de datos estean libres para transmitir os seus datos.

Optimizacións no Sistema Bancario

Ao canalizar coidadosamente as solicitudes a todos os bancos dun rango, o controlador de memoria pode garantir un uso óptimo dos pinos de datos tanto dos chips DRAM como da canle en xeral. Por exemplo, supoñamos que dous comandos de lectura a dous bancos se solapan de xeito que a segunda operación de lectura quedaría esperando a que se liberasen os pinos de datos da primeira. Nese caso, pódese inserir unha operación de actualización nun ou máis bancos que non estean en uso activo nese momento.

Conclusión

Dentro dun chip DRAM, hai varios bancos. Cada banco pode ser operado de forma independente, aínda que todos comparten pins de datos. Isto significa que as operacións de acceso e actualización poden canalizarse, pero os datos reais que se escriben ou lien só poden ser recibidos ou enviados por un banco á vez. Cada banco esténdese perfectamente por todos os chips DRAM nun rango, e estes chips actúan ao paso. Usar bancos, especialmente cando o acceso está optimizado, axuda a maximizar o uso dos pinos de datos cando hai unha carga suficientemente pesada para que iso sexa posible. Non esquezas compartir os teus comentarios a continuación.

Aprende o que é SMPS e o significado das diferentes clasificacións de eficiencia antes de escoller un SMPS para o teu ordenador.

Imos afondar nun tema cada vez máis importante no mundo da ciberseguridade: a seguridade baseada no illamento. Este enfoque para

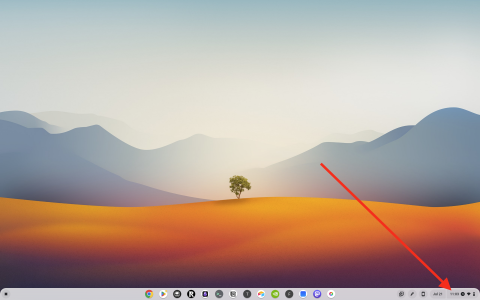

Hoxe imos afondar nunha ferramenta que pode automatizar tarefas de clic repetitivos no teu Chromebook: o Clicker automático. Esta ferramenta pode aforrar tempo e

Resolve un problema no que o teu robot aspirador Roomba se detén, se pega e segue xirando.

Obtén respostas á pregunta Por que non se acende o meu Chromebook? Nesta guía útil para usuarios de Chromebook.

O Steam Deck ofrece unha experiencia de xogo robusta e versátil ao teu alcance. Non obstante, para optimizar o teu xogo e garantir o mellor posible

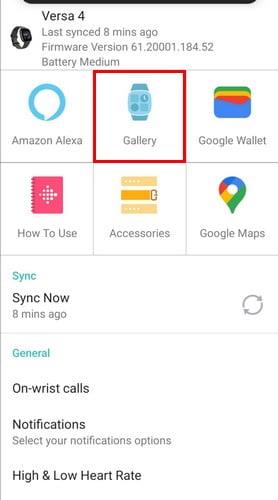

Cambia a esfera do teu Fitbit Versa 4 para darlle ao teu reloxo un aspecto diferente todos os días de forma gratuíta. Mira o rápido e sinxelo que é.

Aprende a denunciar a un estafador a Google para evitar que estafe a outros con esta guía.

Necesitas eliminar a GPU do teu PC? Únete a min mentres explico como eliminar unha GPU do teu PC nesta guía paso a paso.

O hombro surf é unha clase de ataque de enxeñería social. Implica que un atacante recompila información mirando a túa pantalla.