Què és SMPS?

Apreneu què és SMPS i el significat de les diferents classificacions d'eficiència abans de triar un SMPS per al vostre ordinador.

Qualsevol instrucció del processador té diverses etapes per al seu funcionament. Cada una d'aquestes etapes requereix un únic cicle de CPU per completar-se. Aquestes etapes són l'obtenció d'instruccions, la descodificació d'instruccions, l'execució, l'accés a la memòria i l'escriptura. Respectivament, aquests obtenen la instrucció que cal completar, separen l'operació dels valors que s'estan operant, executen el procés, obren el registre on s'escriurà el resultat i escriuen el resultat al registre obert.

Processadors històrics en ordre

Als primers ordinadors, la CPU no utilitzava cap canal d'instruccions. En aquestes CPU, cada operació d'un sol cicle havia de passar per a cada instrucció. Això significava que es necessitaven cinc cicles de rellotge perquè la instrucció mitjana es processés completament abans que es pogués iniciar la següent. És possible que algunes operacions no hagin d'escriure cap resultat en un registre, el que significa que es poden saltar les etapes d'accés a la memòria i d'escriptura.

En un processador subescalar sense canalització, cada part de cada instrucció s'executa en ordre.

Tanmateix, hi ha un problema a l'aguait quan s'executa una instrucció completa en ordre abans de poder passar a la següent instrucció. El problema és la falta de memòria cau. La CPU emmagatzema les dades que està processant activament al registre. S'hi pot accedir amb una latència d'un cicle. El problema és que el registre és petit perquè està integrat al nucli del processador. La CPU ha d'anar a la memòria cau L1 més gran però més lenta si les dades encara no s'han carregat. Si no hi és, ha d'anar de nou a la memòria cau L2 més gran i més lenta. El següent pas és la memòria cau L3; l'última opció és la memòria RAM del sistema. Cadascuna d'aquestes opcions requereix cada cop més cicles de CPU per comprovar.

Ara, aquesta latència addicional addicional pot ser un gran problema en un sistema que ha de completar cada instrucció en ordre abans de començar la següent instrucció. El que havia estat un processador de 5 cicles per instrucció, de sobte es pot quedar pendent d'una instrucció durant desenes o centenars de cicles de rellotge. Mentrestant, no pot passar res més a l'ordinador. Tècnicament, això es pot alleujar una mica tenint dos nuclis independents. Res, però, els impedeix fer el mateix, potencialment simultàniament. Així que baixar per la ruta multinucli no soluciona això.

El gasoducte RISC clàssic

RISC són les sigles de Reduced Instruction Set Computer . És un estil de disseny de processador que optimitza el rendiment facilitant la descodificació de cada instrucció. Això es compara amb CISC o Complex Instruction Set Computer, que dissenya conjunts d'instruccions més complexos que permeten que siguin necessàries menys instruccions per realitzar les mateixes tasques.

El disseny clàssic RISC inclou una canalització d'instruccions. En lloc d'executar qualsevol de les cinc etapes d'instrucció en un cicle determinat, el pipeline permet que es realitzin les cinc etapes. Per descomptat, no podeu executar les cinc etapes d'una instrucció en un cicle. Però podeu posar a la cua cinc instruccions consecutives amb un desplaçament d'una etapa cadascuna. D'aquesta manera, es pot completar una instrucció nova cada cicle de rellotge. Ofereix un augment potencial del rendiment 5 vegades per a un augment relativament baix de la complexitat del nucli.

En un processador escalar canalitzat, cada etapa d'execució d'instruccions es pot realitzar una vegada per cicle de rellotge. Això permet un rendiment màxim d'una instrucció completada per cicle.

Els processadors que no tenen un pipeline només poden ser subescalars, ja que no poden executar una instrucció completa per cicle. Amb aquesta canalització principal de cinc etapes, podeu crear una CPU escalar que pugui completar una instrucció per a cada procés. En crear pipelines encara més amplis, podeu crear CPU superescalars que puguin executar més d'una instrucció per cicle de rellotge. Per descomptat, encara hi ha problemes potencials.

Encara seqüencial

Res d'això resol el problema d'esperar molts cicles per obtenir una resposta quan cal consultar els diferents nivells de memòria cau i RAM. També introdueix un nou problema. Què passa si una instrucció es basa en la sortida de la instrucció anterior? Aquests problemes es resolen de manera independent amb un despatxador avançat. Planifica acuradament l'ordre d'execució de manera que cap instrucció que depengui de la sortida d'un altre estigui massa a prop. També gestiona els errors de memòria cau aparcant una instrucció i substituint-la a la canalització per altres instruccions que estiguin a punt per executar-se i que no requereixin el seu resultat, reprèn la instrucció quan estigui a punt.

Aquestes solucions poden funcionar amb processadors sense canalització, però són necessàries per a un processador superescalar que executa més d'una instrucció per rellotge. Un predictor de branca també és molt útil, ja que pot intentar predir el resultat d'una instrucció amb més d'un resultat potencial i continuar assumint que és correcte tret que es demostri el contrari.

Conclusió

Un pipeline permet utilitzar totes les capacitats diferents del processador en cada cicle. Ho fa executant diferents etapes d'instruccions diferents simultàniament. Això ni tan sols afegeix molta complexitat al disseny de la CPU. També obre el camí per permetre que més d'una instrucció realitzi una única etapa per cicle.

Apreneu què és SMPS i el significat de les diferents classificacions d'eficiència abans de triar un SMPS per al vostre ordinador.

Obteniu respostes a la pregunta: Per què el meu Chromebook no s'encén? En aquesta guia útil per als usuaris de Chromebook.

Obteniu informació sobre com informar d'un estafador a Google per evitar que estafeu altres persones amb aquesta guia.

Solucioneu un problema en què el vostre robot aspirador Roomba s'atura, s'enganxa i segueix girant.

El Steam Deck ofereix una experiència de joc robusta i versàtil al teu abast. Tanmateix, per optimitzar el vostre joc i garantir el millor possible

Anàvem a aprofundir en un tema que cada cop és més important en el món de la ciberseguretat: la seguretat basada en l'aïllament. Aquest enfocament a

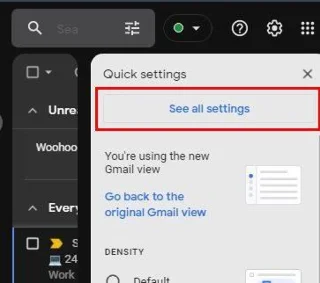

Avui anàvem a aprofundir en una eina que pot automatitzar tasques de clics repetitius al vostre Chromebook: el clic automàtic. Aquesta eina us pot estalviar temps i

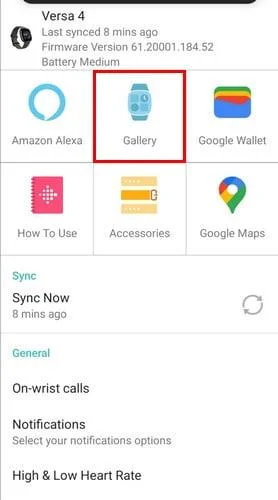

Canvia la cara del rellotge del teu Fitbit Versa 4 per donar-li un aspecte diferent cada dia de manera gratuïta. Mireu que fàcil i ràpid és.

Necessites treure la GPU del teu ordinador? Uneix-te a mi mentre t'explico com eliminar una GPU del teu PC en aquesta guia pas a pas.

El surf a l'espatlla és una classe d'atac d'enginyeria social. Implica que un atacant recopila informació mirant la pantalla.