Què és SMPS?

Apreneu què és SMPS i el significat de les diferents classificacions d'eficiència abans de triar un SMPS per al vostre ordinador.

Hi ha moltes capes diferents per abordar la DRAM. DIMM és probablement el més conegut, amb un DIMM ( Dual In-line Memory Module ) que és una memòria RAM. Finalment, la memòria es gestiona mitjançant una adreça de fila i columna. Tanmateix, hi ha moltes capes més entremig. S'accedeix a la memòria per canals. Cada canal és totalment independent i pot transmetre dades al mateix temps.

Nota: tot i que els canals són independents, funcionen de manera sincronitzada i estan sincronitzats. És essencial assegurar-se que cada canal poblat funcioni a la mateixa velocitat i tingui els horaris exactes. Idealment, tots els DIMM connectats haurien de ser idèntics i d'un kit. La memòria RAM no idèntica pot causar problemes d'estabilitat. Si es connecten DIMM de diferents velocitats, el més ràpid es limitarà a la velocitat més lenta.

En un DIMM, teniu un o més rangs de xips DRAM. Tots els xips d'un rang s'aborden alhora i es presenten essencialment a la CPU com un xip DRAM més gran. Això funciona perquè les dades es reparteixen per tots els xips DRAM d'un rang. Per exemple, un canal té una amplada de 64 bits i un xip DRAM té una amplada de 8 bits. Es necessiten 8 xips DRAM per proporcionar 64 bits de dades als pins de dades. El rang es defineix essencialment per la selecció de xips, que actua com a bifurcador de les fitxes sota el seu control. Cada xip té diversos bancs.

Banca en DRAM

En un sol xip DRAM, hi ha diversos bancs. L'especificació DDR4 assigna 4 bits als bancs d'adreça, permetent 16 bancs per xip DRAM. Cada banc és generalment independent i pot estar en qualsevol fase del cicle d'accés/actualització. Tots els bancs només tenen un conjunt de pins de dades. Aquesta configuració limita el xip DRAM a tenir només un banc que transmet o rep dades per cicle de rellotge. També permet una canalització forta, que, amb una càrrega suficient, permet que aquests pins de dades estiguin actius en la majoria, si no en tots, els cicles de rellotge en lloc de quedar-se inactius mentre s'obre una fila nova.

Una altra cosa clau que cal saber sobre els bancs és que estan completament sincronitzats entre una sèrie de xips DRAM. Aquesta sincronització és tan completa que es pot considerar que els bancs abasten tots els xips DRAM del rang.

Un exemple treballat

Utilitzem un exemple; en aquest exemple, una operació de lectura arriba a un rang per accedir al banc 2, fila 3, columna 4. Tots els xips DRAM del rang obriran la fila tres, la columna quatre, al segon banc. Cadascun retornarà 8 bits de dades. La selecció de xip que defineix el rang concatenarà les dades que rep en el format ample de 64 bits del canal i les enviarà al controlador de memòria de la CPU.

Portant l'exemple una mica més enllà, al mateix temps que el banc 2 gestiona la sol·licitud de lectura, el banc tres pot realitzar una operació d'actualització. A més, el banc 1 pot tancar la seva fila oberta per preparar-la per obrir-ne una de nova. El banc 7 pot completar una operació de lectura al mateix temps. Tanmateix, no pot enviar les dades simultàniament, ja que tots els bancs comparteixen el mateix conjunt de pins de dades. El banc 7 ha d'esperar que els pins de dades estiguin lliures per transmetre les seves dades.

Optimitzacions en el sistema bancari

En canalitzar acuradament les sol·licituds a tots els bancs d'un rang, el controlador de memòria pot garantir un ús òptim dels pins de dades tant dels xips DRAM com del canal en general. Per exemple, suposem que dues ordres de lectura a dos bancs es superposarien de manera que la segona operació de lectura es deixaria esperant que els pins de dades s'alliberin de la primera. En aquest cas, es pot inserir una operació d'actualització en un o més bancs que no estiguin en ús actiu en aquell moment.

Conclusió

Dins d'un xip DRAM, hi ha diversos bancs. Cada banc es pot operar de manera independent, tot i que tots comparteixen pins de dades. Això vol dir que les operacions d'accés i actualització es poden canalitzar, però les dades reals que s'escriuen o llegeixen només les pot rebre o enviar un banc alhora. Cada banc s'estén perfectament per tots els xips DRAM d'un rang, i aquests xips actuen en un mateix pas. L'ús de bancs, especialment quan l'accés està optimitzat, ajuda a maximitzar l'ús dels pins de dades quan hi ha una càrrega prou pesada perquè això sigui possible. No us oblideu de compartir els vostres comentaris a continuació.

Apreneu què és SMPS i el significat de les diferents classificacions d'eficiència abans de triar un SMPS per al vostre ordinador.

Obteniu respostes a la pregunta: Per què el meu Chromebook no s'encén? En aquesta guia útil per als usuaris de Chromebook.

Obteniu informació sobre com informar d'un estafador a Google per evitar que estafeu altres persones amb aquesta guia.

Solucioneu un problema en què el vostre robot aspirador Roomba s'atura, s'enganxa i segueix girant.

El Steam Deck ofereix una experiència de joc robusta i versàtil al teu abast. Tanmateix, per optimitzar el vostre joc i garantir el millor possible

Anàvem a aprofundir en un tema que cada cop és més important en el món de la ciberseguretat: la seguretat basada en l'aïllament. Aquest enfocament a

Avui anàvem a aprofundir en una eina que pot automatitzar tasques de clics repetitius al vostre Chromebook: el clic automàtic. Aquesta eina us pot estalviar temps i

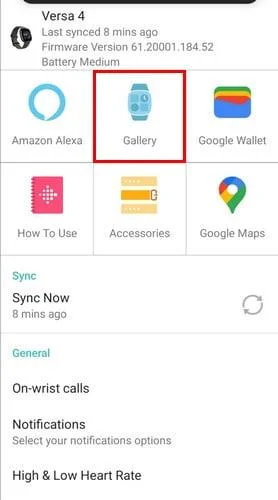

Canvia la cara del rellotge del teu Fitbit Versa 4 per donar-li un aspecte diferent cada dia de manera gratuïta. Mireu que fàcil i ràpid és.

Necessites treure la GPU del teu ordinador? Uneix-te a mi mentre t'explico com eliminar una GPU del teu PC en aquesta guia pas a pas.

El surf a l'espatlla és una classe d'atac d'enginyeria social. Implica que un atacant recopila informació mirant la pantalla.