Alt om iOS 26

Apple har introduceret iOS 26 – en større opdatering med et helt nyt design med frostet glas, smartere oplevelser og forbedringer af velkendte apps.

CPU'er er utroligt komplekse dyr. Der er mange sammenkoblede dele, som alle skal arbejde i perfekt forening for at opnå de niveauer af ydeevne, vi ser. En af nøglefunktionerne ved en CPU er cachen. Det er ikke en prangende funktion. Det annoncerer ikke så godt som core count eller peak boost frekvens. Det er dog afgørende for ydeevnen.

Hvorfor cache?

Moderne CPU'er er utrolig hurtige. De udfører mere end fem milliarder operationer hvert sekund. Det er svært at holde CPU'en fodret med data, når den kører så hurtigt. RAM'en har nok kapacitet til at forsyne CPU'en med data. Den kan endda overføre data hvert sekund, takket være meget høje båndbredder. Det er dog ikke problemet. Problemet er latens.

RAM kan reagere meget hurtigt. Problemet er, at "meget hurtigt" er lang tid, når du gør fem milliarder ting hvert sekund. Selv den hurtigste RAM har en latency på over 60 nanosekunder. Igen lyder 60 nanosekunder som ingen tid overhovedet. Problemet er, at hvis CPU'en kørte ved 1GHz, ville det tage 1ns at fuldføre en cyklus. Med avancerede CPU'er, der rammer 5,7 GHz, er det én cyklus hver 175 picosekunder. Hvordan ser de 60 nanosekunders latency ud nu? Det er 342 cyklusser med latens.

Den slags latency ville være en dræber for enhver CPU-ydelse. For at komme uden om det, bruges en cache. Cachen placeres på selve CPU-dysen. Det er også meget mindre end RAM og bruger en anden struktur, SRAM frem for DRAM. Dette gør det meget hurtigere at reagere end hovedsystemets RAM. Cachen er typisk lagdelt, hvor L1, L2 og L3 bruges til at betegne de lag, der kommer længere og længere fra CPU-kernerne. Lavere niveauer er hurtigere, men mindre. L1 kan have en latenstid på fire eller fem clock-cyklusser, meget bedre end 342.

Men nogle CPU'er nævner en L0?

Terminologien for L1, L2 og L3 er ret standard. Den vage forståelse af, hvad de betyder og gør, er relativt almindelig, selv på tværs af CPU-leverandører. Dette er fordi de er styret af materiale og elektrisk fysik; ikke meget kan ændre sig. Du kan have en hurtig cache eller en stor cache, ikke begge dele. Den skal være større, hvis du deler en cache mellem flere kerner. Til det formål har L1 og L2 en tendens til at være kernespecifikke. Den større L3-cache har en tendens til at blive delt mellem nogle eller alle kerner på CPU'en eller chiplet.

Som du sikkert kan gætte, er L0 relateret til caching, men er blevet skubbet ind i navneskemaet bagefter. Det hjælper dog ikke at forstå, hvad det betyder. Du kan dog sikkert gætte nogle ting. Det vil være begrænset til én kerne, det vil være lille, og det vil være hurtigt. Det andet navn det går under kan hjælpe lidt; det er micro-op cache.

I stedet for at cache data fra hukommelsen eller fulde instruktioner, cacher L0 mikrooperationer. Som vi for nylig beskrev , er en mikrooperation en funktion af moderne CPU'er. Instruktioner i x86 og andre ISA'er er store, komplekse og udfordrende for at passe effektivt ind i en pipeline. Du kan pipeline dem meget mere effektivt, hvis du opdeler dem i mikrooperationer. I nogle tilfælde kan du endda gruppere flere mikrooperationer, selv fra forskellige instruktioner, i en enkelt mikrooperation for at opnå både en ydeevneforbedring og effektreduktion.

CPU Architecture ft Micro-Op Cache

For at udføre en instruktion afkoder en moderne CPU den. Dette indebærer at opdele instruktionen i dens bestanddele af mikrooperationer og bestemme de hukommelsesplaceringer, der skal refereres til. Mange software bruger lignende funktionalitet regelmæssigt og kan ofte genbruge den samme kode i en løkke eller fra en kaldt funktion. Det betyder, at de nøjagtige instruktioner kan kaldes igen og igen. Det betyder så, at de samme mikrooperationer bliver kaldt igen og igen. Og hvis de samme mikrooperationer er nødvendige gentagne gange, kan de cachelagres. Caching af mikrooperationer kan reducere belastningen på instruktionsdekoderne, reducere strømforbruget eller hjælpe med at fylde rørledningen op hurtigere.

Cachen skal holdes lille, men når den administreres omhyggeligt, kan den tilgås med en enkelt eller endda ingen cyklusforsinkelse. Dette kan være nok til at forhindre behovet for at overtage 4-cyklus latency til L1 cachen og kommer uden cache-miss straf.

Konklusion

L0 cache er et andet navn for micro-op cachen. Det kan være en del af moderne CPU'er, der bruger mikrooperationer. Det rummer typisk et par tusinde poster og har kapaciteter angivet i antal poster i stedet for bytes. L0 kan tilgås hurtigere end L1, typisk med en 1- eller 0-cyklus latency. Caching af mikrooperationer reducerer belastningen på instruktionsdekoderne, især i kode, der gør god brug af loops eller funktioner.

Apple har introduceret iOS 26 – en større opdatering med et helt nyt design med frostet glas, smartere oplevelser og forbedringer af velkendte apps.

Studerende har brug for en specifik type bærbar computer til deres studier. Den skal ikke kun være kraftig nok til at præstere godt i deres valgte fag, men også kompakt og let nok til at kunne bæres rundt hele dagen.

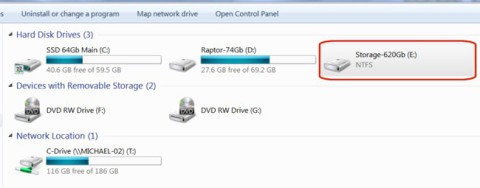

I denne artikel vil vi guide dig til, hvordan du genvinder adgang til din harddisk, når den fejler. Lad os følge med!

Ved første øjekast ligner AirPods alle andre ægte trådløse øretelefoner. Men alt dette ændrede sig, da et par mindre kendte funktioner blev opdaget.

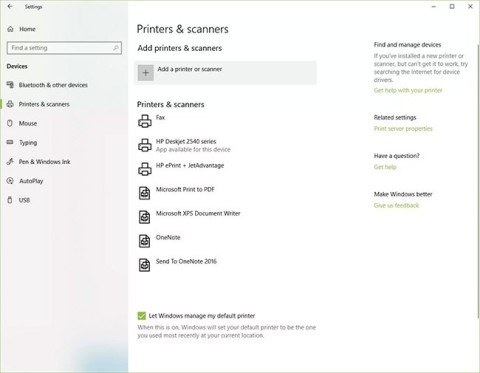

Det er enkelt at tilføje en printer til Windows 10, selvom processen for kablede enheder vil være anderledes end for trådløse enheder.

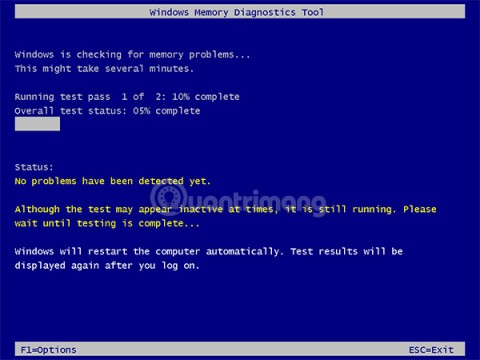

Som du ved, er RAM en meget vigtig hardwaredel i en computer, der fungerer som hukommelse til at behandle data og er den faktor, der bestemmer hastigheden på en bærbar computer eller pc. I artiklen nedenfor vil WebTech360 introducere dig til nogle måder at kontrollere for RAM-fejl ved hjælp af software på Windows.

Har du lige købt en SSD i håbet om at opgradere din computers interne lager, men ved ikke, hvordan du installerer SSD? Læs denne artikel nu!

Sådan aktiveres scanning på Canon Pixma MG5220, når du er løbet tør for blæk.

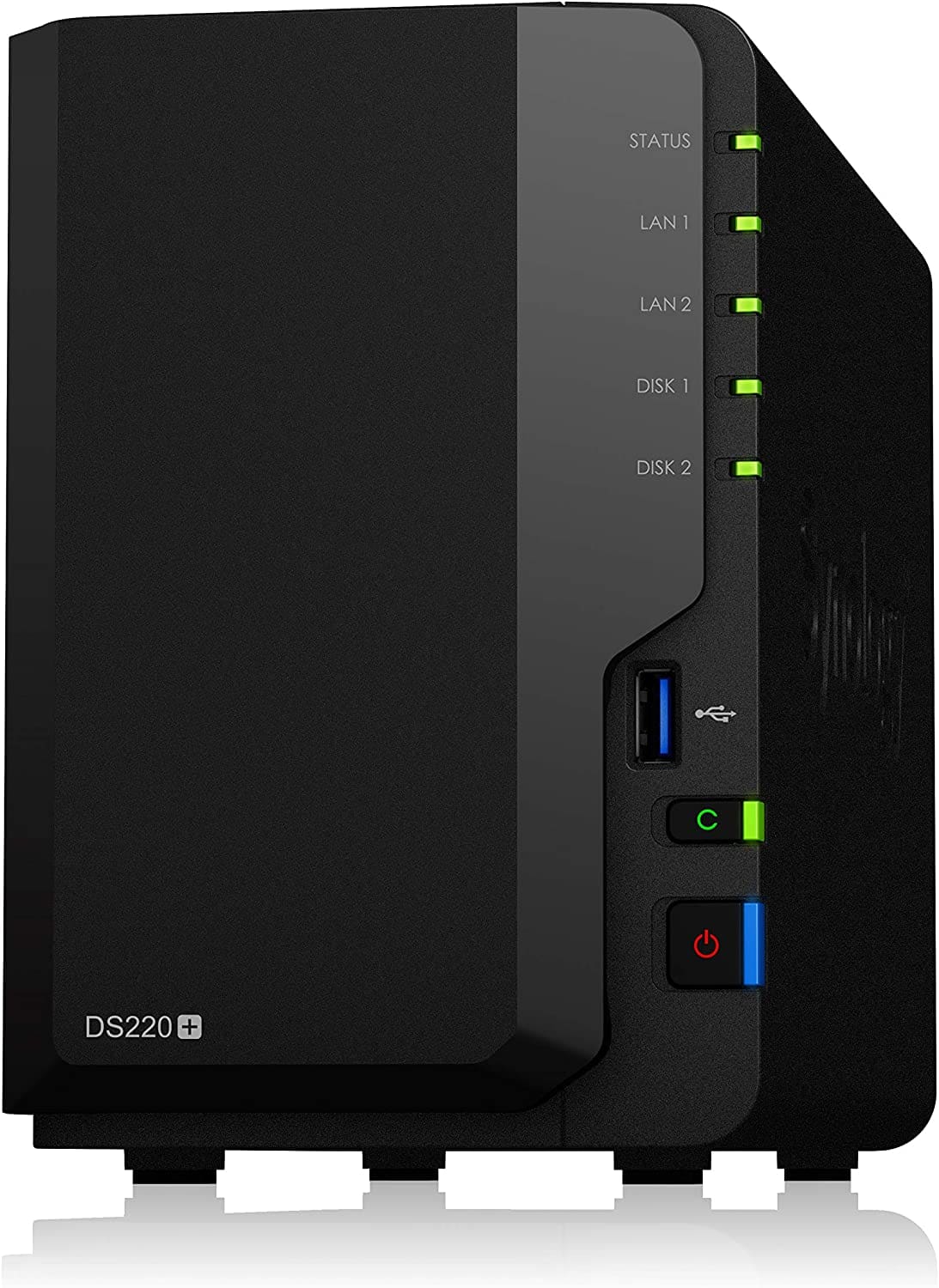

Uanset om du leder efter en NAS til dit hjem eller kontor, så tjek denne liste over de bedste NAS lagringsenheder.

Hvis din Powerbeats Pro ikke oplades, skal du bruge en anden strømkilde og rengøre dine earbuds. Lad etuiet være åbent, mens du oplader dine earbuds.