Viss par iOS 26

Apple ir ieviesis iOS 26 – būtisku atjauninājumu ar pavisam jaunu matēta stikla dizainu, viedākām lietošanas iespējām un uzlabojumiem jau pazīstamās lietotnēs.

Vēsturiski CPU ir bijušas perfekti secīgas mašīnas. Tas ir ļoti loģiski un viegli saprotami, taču tas var būt veiktspējas problēma. Gadu gaitā ir veikti daudzi ģeniāli CPU konstrukciju pielāgojumi, lai iegūtu pēc iespējas lielāku veiktspēju no silīcija plāksnēm. Tomēr viens no interesantākajiem ir neatbilstoša izpilde. Ārpus kārtības izpildes centrālajos procesoros instrukcijas nav obligāti jāizpilda tādā secībā, kādā tās tiek izdotas.

Apstāšanās kārtībā

Galvenā veiktspējas problēma, ar kuru saskaras pasūtījuma centrālais procesors, tiek saukta par konveijera aizturi. Tas notiek, ja instrukcija ir atkarīga no atmiņas, bet šī atmiņa nav tieši pieejama reģistrā. Šajā gadījumā CPU ir jāatrod šī vērtība atmiņā. Vispirms tiek pārbaudīta CPU kešatmiņa, jo tas ir ātrākais atmiņas līmenis. Ja vērtības nav, tiek pārbaudīta sistēmas RAM. Šajā laikā centrālajam procesoram ir jādarbojas dīkstāvē, jo no atmiņas atkarīgā instrukcija ir jāpabeidz secībā pirms tālāk norādītajām instrukcijām.

Cauruļvada iegrimes ietekme uz veiktspēju var nebūt tik slikta, taču tā var būt arī salīdzinoši nopietna. Piemēram, L1 kešatmiņa parasti var atgriezt rezultātu 5 CPU ciklu lielumā. L2 kešatmiņa var aizņemt 20 ciklus, L3 aptuveni 200 ciklus un sistēmas RAM aptuveni 400 ciklus. Ņemot vērā, ka centrālais procesors var darboties aptuveni 5 GHz, tas ir, 5 miljardus takts ciklu sekundē, pat 400 cikli nav tik slikti (0,000008%). Bet, ja jums ir daudz instrukciju, kas attiecas uz datiem, kas atrodas tālāk kešatmiņas līmeņos, kumulatīvā ietekme var izraisīt ievērojamu palēnināšanos.

Ārpus kārtības izpilde un reģistra pārdēvēšana

Ārpuskārtas izpilde ir paņēmiens, kas ļauj plānotājam pārkārtot instrukcijas savā rindā. Veicot šo pārkārtošanu, tā var izvēlēties piešķirt prioritāti noteiktiem pavedieniem salīdzinājumā ar citiem. Tas var arī novirzīt norādījumus atpakaļ rindā, ja tiem ir datu atkarība, kas vēl nav izpildīta. Tas pēc iespējas novērš cauruļvadu iestrēgšanu, samazinot dīkstāves ciklus.

Ārpuskārtas izpildei ir nepieciešama funkcija, ko sauc par reģistra pārdēvēšanu. CPU var piekļūt datiem, kas atrodas reģistros viena cikla laikā. Reģistrus izmanto lasāmo un rakstīto datu glabāšanai. Tomēr ir svarīgi nodrošināt, lai dators kopumā redzētu visu notiekošo loģiskā secībā, nevis neregulārā, CPU cikla optimizētā secībā. Lai to iespējotu, CPU ir daudz vairāk loģisko reģistru, nekā prasa CPU arhitektūra.

Datus, kas jāizraksta, bet kuriem ir “agrāka” instrukcija, kas vēl nav aizpildīta, tiek ievietoti turēšanas reģistrā. Šie dati netiek pārsūtīti uz citu reģistru, kad pasūtījums ir sakārtots pats par sevi. Tā vietā saimniecības reģistra nosaukums tiek mainīts uz tā reģistra nosaukumu, kurā tam vajadzētu būt. Tas ir nedaudz līdzīgs deserta pagatavošanai pirms pamatēdiena, bet pēc tam glabāšanai ledusskapī, līdz ir pienācis laiks to pasniegt.

Šie loģiskie reģistri ir pilnīgi neadresēti. CPU reāli var risināt tikai tos loģiskos reģistrus, kuriem pašlaik ir kopīgs arhitektūras reģistru nosaukums. Tomēr centrālais procesors arī tos pietiekami labi apzinās, ka, ja citas pārkārtotās instrukcijas balstās uz loģiskā turēšanas reģistra datiem, tās var izmantot tos, nevis “novecojušos” arhitektūras reģistra datus konkrētajā empīriskajā laikā.

Atmiņas barjeras

Atmiņas barjera – saukta arī par membar, atmiņas žogu vai žoga instrukciju – ir instrukcija datora kodā. Tas ļauj programmētājam ieviest pasūtīšanas ierobežojumus atmiņas operācijām, kas izdotas pirms un pēc atmiņas barjeras. Atmiņas barjera uzdod CPU plānotājam nodrošināt, lai visas instrukcijas tiktu apstrādātas pirms jebkādas instrukcijas pēc barjeras. Tas tiek darīts, lai nodrošinātu, ka svarīgas darbības tiek pabeigtas pareizā secībā.

Parasti mūsdienu datoros tas nav nepieciešams. Nepareiza izpilde un reģistra pārdēvēšana ir labi izveidotas un nobriedušas jomas. Tomēr atmiņas barjera var būt noderīga vecākiem, mazāk sarežģītiem procesoriem, kas nav kārtībā vai tiek izmantoti kritiskās atmiņas operācijās.

Atmiņas šķēršļi var izraisīt veiktspējas traucējumus. Tas ir tāpēc, ka tie aktīvi neļauj CPU plānotājam optimizēt noteiktas instrukciju plūsmas daļas. Tas palielina cauruļvada iestrēgšanas iespēju.

Secinājums

Atmiņas barjera ir instrukcija, kas nodrošina atmiņas darbību pasūtīšanas ierobežojumu. Tas ir svarīgi, jo ārpus kārtas izpildes procesori var pārkārtot noteiktas instrukcijas. Lai gan reģistra pārdēvēšana ir plaši pazīstama kā metode atmiņas integritātes nodrošināšanai šajā vidē, var būt noderīgi to nodrošināt manuāli.

Atmiņas barjera liek CPU plānotājam nodrošināt, lai instrukcijas tiktu izpildītas pirms jebkādas instrukcijas pēc barjeras. Tas novērš atmiņas darbību pārkārtošanu. Tas arī neļauj CPU optimizēt instrukciju plūsmu, kas var ietekmēt veiktspēju.

Apple ir ieviesis iOS 26 – būtisku atjauninājumu ar pavisam jaunu matēta stikla dizainu, viedākām lietošanas iespējām un uzlabojumiem jau pazīstamās lietotnēs.

Studentiem studijām ir nepieciešams noteikta veida klēpjdators. Tam jābūt ne tikai pietiekami jaudīgam, lai labi darbotos izvēlētajā specialitātē, bet arī pietiekami kompaktam un vieglam, lai to varētu nēsāt līdzi visu dienu.

Šajā rakstā mēs parādīsim, kā atgūt piekļuvi cietajam diskam, ja tas neizdodas. Sekosim līdzi!

No pirmā acu uzmetiena AirPods izskatās gluži kā jebkuras citas īstas bezvadu austiņas. Taču tas viss mainījās, kad tika atklātas dažas maz zināmas funkcijas.

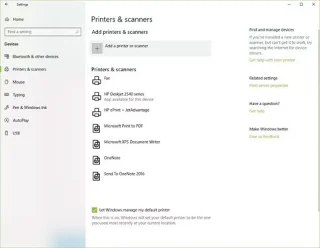

Printera pievienošana operētājsistēmai Windows 10 ir vienkārša, lai gan vadu ierīču process atšķirsies no bezvadu ierīču procesa.

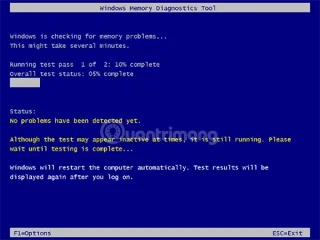

Kā zināms, RAM ir ļoti svarīga datora aparatūras daļa, kas darbojas kā atmiņa datu apstrādei un ir faktors, kas nosaka klēpjdatora vai datora ātrumu. Zemāk esošajā rakstā WebTech360 iepazīstinās jūs ar dažiem veidiem, kā pārbaudīt RAM kļūdas, izmantojot programmatūru operētājsistēmā Windows.

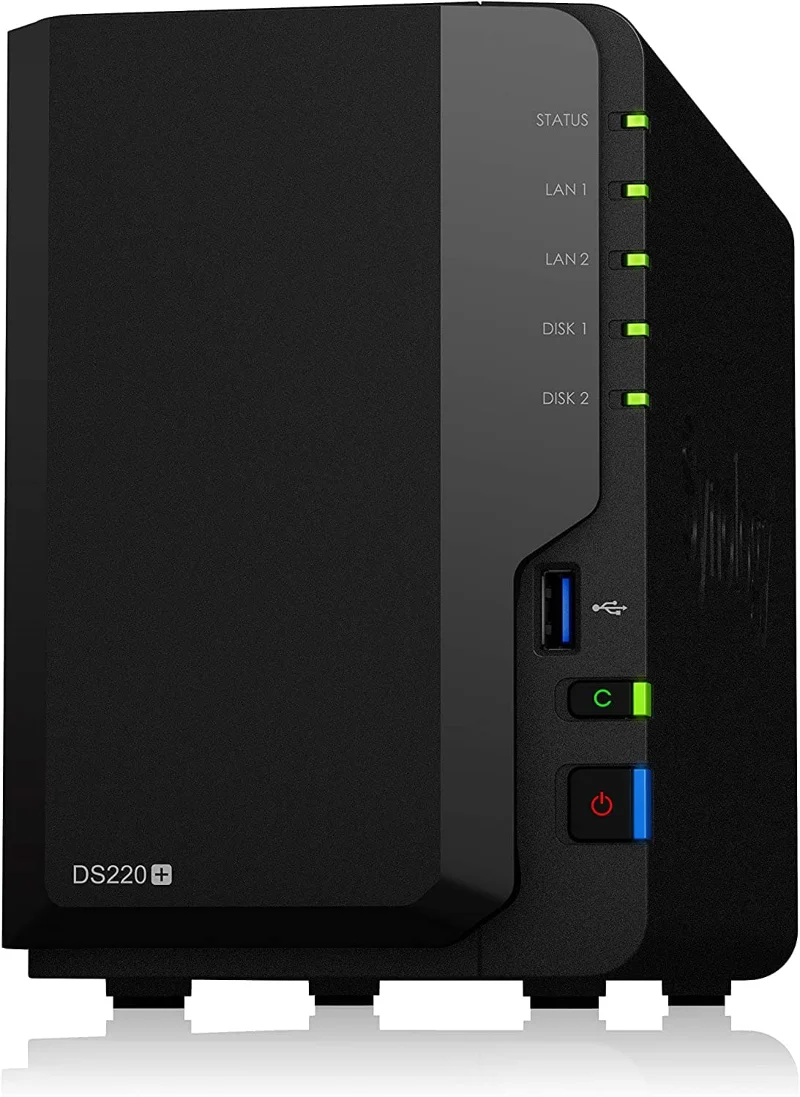

Ja meklējat NAS risinājumu mājai vai birojā, iepazīstieties ar šo labāko NAS uzglabāšanas iekārtu sarakstu.

Vai jums ir grūtības noskaidrot, kāda IP adrese jūsu drukātājam tiek izmantota? Mēs parādīsim, kā to atrast.

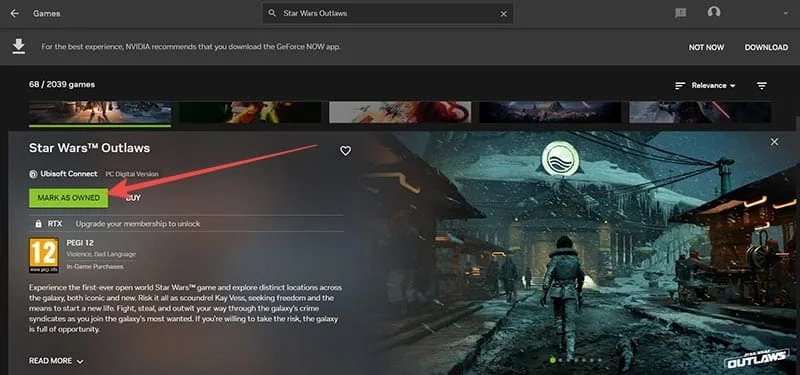

Jūs gatavojaties vakaram ar spēlēšanu, un tas būs liels vakars – jūs tikko esat iegādājies “Star Wars Outlaws” GeForce Now straumēšanas pakalpojumā. Uzziniet vienīgo zināmo risinājumu, kas parāda, kā novērst GeForce Now kļūdas kodu 0xC272008F, lai jūs varētu sākt spēlēt Ubisoft spēles atkal.

Uzziniet dažus iespējamos iemeslus, kāpēc jūsu klēpjdators pārkarst, kā arī padomus un trikus, lai izvairītos no šīs problēmas un uzturētu savu ierīci vēsu.